# 薄膜デバイスとニューロモルフィックシステムの研究・応用

メンバー：田丸敦也 中村凌成 岩本康太 青山文二 山本啓太 大島涼 大平涼太 高木悠真

## 1. 本グループの研究目的

ソフトウェア上でのAI開発は年々進み、AIや大規模言語モデルなどが社会に浸透

→ 伴って電力消費も爆発的に増加

2018年時点での世界全体のIPトラフィック予測(\*1)によると2018年比で2030年には30倍2050年にはなんと**4,000倍**の消費電力に！

そこで、脳の模倣を「ハードウェア」で行い、低消費電力・高ロバスト性の人工知能を実現することが目的である。

## 2. R-Gap活動概要

ニューロモルフィックデバイスの研究・応用を目的に、R-Gap期間中においては、自主研究に加え、奈良先端科学技術大学院大学（NAIST）および国立成功大学（NCKU）における学習・研究活動を実施した。

## 3. 自主研究概要

- FeFET研究

- ESRを用いた酸素空孔の検出

- memristor+memcapacitorによる高効率ニューロモルフィックデバイスの研究

- 負性微分抵抗memristorの研究

- memristorの研究

## 4.1 NAISTでの活動

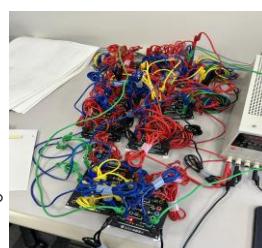

リレー、スイッチ、電源を用いてコンピュータの基本動作を体験した。

まずLEDを使って電源やリレーの動作確認を行い、1桁の2進数加算器を作成。

これを拡張して複数桁の加算器（全加算器）を構築した。

続いてラッチ回路やフリップフロップを作成。

加算器と組み合わせてスイッチ操作で1ずつ加算されるカウンタを実現。

クロック回路を作成し、実際に演算を行った。

画像 実際に使用したボード

画像 作成した全加算器

## 4.2 NAISTでの活動

演算・記憶・時間制御といったコンピュータの基本動作原理を理解した。

写真 作成した回路(左上)とのショット

また、中島教授から現在の半導体業界、コンピュータアーキテクチャ、ニューロモルフィックシステムについて講義を受け、最新技術の動向や自分たちの研究分野への取り組み方について理解を深めた。

## 5. NCKUでの活動

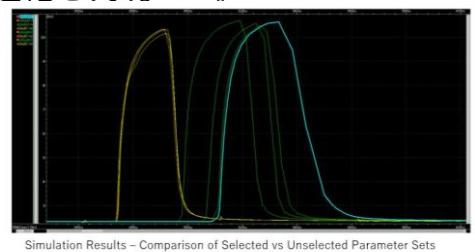

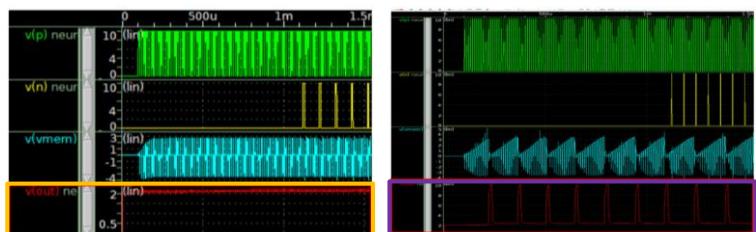

NCKUから提供された回路を基に、H-Spice（回路シミュレーションソフトウェア）を用いて動作解析を行った。

まず、回路におけるスパイク（発火）パルス発生の限界条件を検証した。

画像 シミュレーション結果

左が発火に失敗した際の波形（オレンジ枠内）、右が発火に成功した際の波形（紫色枠内）

シナプス回路からの入力パルスに対して膜電位が上昇し、一定の閾値を超えると**発火**( $v_{out}$ 波形)が生じる。そこで、提供された回路において、どの程度短いパルスまで発火が可能かを、回路パラメータを変化させ解析した。

その結果、パルス幅と無入力時間の比率が発火特性を支配する主要因であることを明らかにした。

次に、回路性能の向上を目的として、Delay Unit内のトランジスタパラメータを調整し、動作特性の最適化を実現した。

これにより、信号遅延の安定化と全体の応答特性の改善が確認された。

(右画像)