# 薄膜デバイスとニューロ モーフィックシステムの 調査・研究

2023 年度プロジェクトリサーチ

# 活動報告

No.09 薄膜デバイスとニューロモーフィックシステムの調査・研究

上尾高範、加隈匠悟、川崎優貴、高橋遼平、 出口蓮、中川聖也、根本萌、堀内厚志

#### 1.目的

現在普及しているコンピュータにはノイマン型アーキテクチャが用いられているが、ノイマン型アーキテクチャには、写真や動画などの非構造化データを効率良く処理できないという弱点や、プロセッサと記憶装置を接続するバスのデータ転送速度がネックとなって性能が向上しない、いわゆるフォン・ノイマン・ボトルネックと呼ばれる弱点がある。そのため、これらの弱点を克服するために、高速な不揮発性メモリ(FeRAM、MRAM、ReRAM、PRAM など)の研究や、非ノイマン型コンピュータ(ニューロモーフィックコンピュータ、量子コンピュータなど)の研究が世界中で盛んに行われており、木村睦研究室においてもこれらの研究が行われている。そこで、このプロジェクトリサーチでは、木村睦研究室にて装置の使い方や測定の仕方を教わりながら一つの薄膜デバイスを作製し特性の測定を行うことで薄膜デバイスやニューロモーフィックシステムの応用について調査、学習する。また、奈良先端科学技術大学院大学(以下、NAIST)や台湾国立成功大学でのインターンシップに参加し、HSPICEに関する理解を深める。またこれらの活動を通して、今後の研究活動がより主体性のあるものとなるよう努力したいと思っている。

#### 2.計画、調査方法

#### 2-1. 木村睦研究室

木村膝研究室にて、薄膜デバイスの作製や特性の測定、世界的な研究開発の状況に関する調査・研究を行う。

各メンバーは複数の研究グループに分かれ、それぞれ調査・研究を行う。

抵抗変化メモリ担当:中川

STDP担当: 堀内

ショットキー+メモリスタ+キャパシタ担当:上尾、高橋、根本、加隈

北海道大学共同研究(ショットキー+メモリスタ+キャパシタ)担当:加隈

TFT・強誘電体担当:川崎、出口

# 2-2. NAIST インターンシップ

HSPICEを用いた回路シミュレーションの学習を行う。

日程:7月10日~14日

担当:上尾、加隈、川崎、高橋、中川、根本、堀内

# 2-3. 台湾国立成功大学インターンシップ

夏期休暇の1週間を活用し、台湾国立成功大学にて薄膜デバイスについて調査・研究する。

日程:9月10日~18日

担当:加隈、川崎、出口、根本、堀内

#### 3.成果

# 3-1.抵抗変化メモリ

#### 3-1-1.研究背景と目的

高い電荷移動度、超高速性、長い保持時間、低消費電力という点で優れていおり、抵抗変化素子やニューロモルフィックシステムの開発に注目されている。これまで GTO などの金属酸化物半導体材料が研究されてきたが Zn-Sn-O ベースにした抵抗変化素子などに関係する研究はほとんど報告されていない。 ZTO は優れた電気特性が確認されている GTO などと似ていて、 ZTO はレアメタルを使わ無くて良く、低コストであり、毒性が低い。これらの事から ZTO は抵抗変化素子やニューロモルフィックシステム開発用のデバイスに応用できる。スパッタリング法で作られるものと同じくらいの性能の良さがある ReRAM をミスト CVD の低コスト、低エネルギー、組成比を容易に変えることができることを活かして作製する。

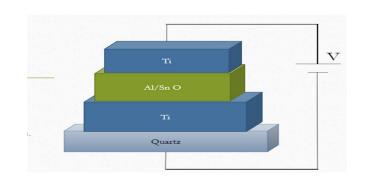

3-1-2.実験方法 [真空蒸着法] 下部,上部電極:Ti 蒸着時間 5 分

[ミスト CVD]

3-1-3.デバイス構造・条件

モル濃度: 0.030mol/L

成膜温度:400°C

キャリアガス: 0.5L/min.

希釈ガス:10L/min.

(1)Al2O3 : Sn2(7:3),(2)Al2O3 : Sn2(3:7)

# 3-1-4. 結果

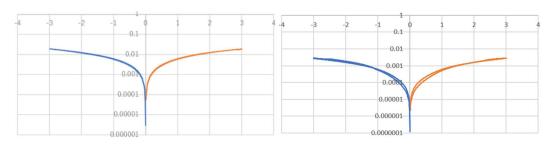

1Al2O3 : SnO2 (7:3) 2Al2O3 : SnO2 (3:7)

図3-1-4-1:Al:Sn=7:3の電気特性

図3-1-4-2: Al:Sn=3:7の電気特性

電気特性を半導体パラメータで比較を行った。2つのグラフを見比べるとAlが多い方に開きがあることが確認することができる。しかし、この開きはごくわずかなものであり、私達が求めている良い特性にはほど遠いと言える。

今後の研究としては、材料や成膜温度、組成比を変え、特に膜の均一に着目して良い特性が得られるように務める。

#### 3-2.STDP

#### 3-2-1.研究背景と目的

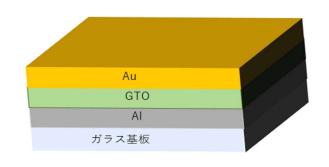

人工知能の分野で、ハードウェアであるニューロモーフィックデバイスを実現することによって、高 消費電力などの問題の解決することを目指す。ニューロモーフィックとは、ニューラルネットワーク (人間の脳の神経細胞であるニューロンとシナプスから構成される神経回路網)を模した電子回路に よって構成されているものである。研究の目標は、スパイキングニューラルネットワークの学習則の 一つである、スパイクタイミング依存シナプス可塑性(STDP)を用いて、低消費電力かつ人間の脳に近 い学習が可能なデバイスの作製することである。シナプスとして Ga-Sn-O(GTO)を、ガラス基板上に 成膜する。そして、時間差をつけてパルスを入力し、その際の電気的特性を測定する。結果、GTO を シナプス素子として用いたSTDP 学習則によるニューロモーフィックデバイスを作製できる可能性を 示す。

3-2-2.実験方法 デバイス構造・条件 実験方法は、以下に示す。

# [真空蒸着装置]

上部 Al 5min

下部 Au 5 min

[RF マグネトロンスパッタリング法]アルゴン酸素比 20:0/20:1/20/0成膜時間 3/10/3

# [半導体パラメータアナライザ]

$\pm 2 \sim 4 \text{ V}$ まで0.5 Vづつ電圧印加し、I-V特性の測定を行った。

#### 3-2-3. 結果と考察

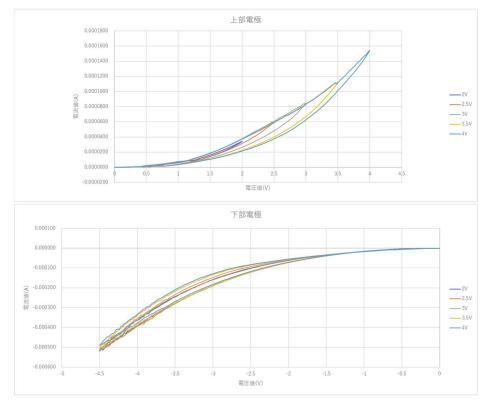

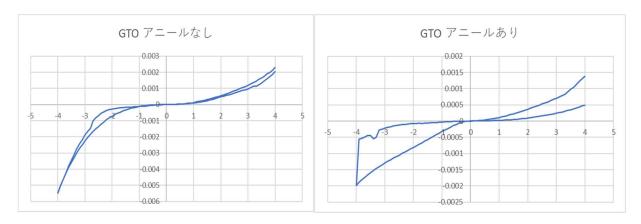

今回実験では、STDP測定をするために、主に上記のデバイスを作成、そしてI-V測定を行った。STD P測定をする前にI-V測定を行い、ちゃんと抵抗変化を行えれるかを調べて、そのデバイスがSTDPに 適しているか状態を調べるたに行っている。

今回の実験でのデータは次のようになる。

今回の、実験での結果は結果としては、抵抗変化率が低いデバイスであった。そのため、STDPに、 使えないデバイスであることが分かる。

今回のデバイスは、上部電極では4Vで、一番抵抗変化が起きた。これに関しては、低い電圧では、抵抗変化が小さく、大きい電圧をかけたときにSTDP特性が出やすいデバイスであることが考えられる。

また、下部電極に関しては、電圧に関係なくほとんどが同じ抵抗変化率であり、電圧の出力に関しても変化しないことが分かる。この結果から、電圧に関係なく、リセット出来る事が分かる。 今後は、デバイスの条件を変化させながら最適なSTDPの結果が出そうなデバイスを作成していきたい。 3-3.ショットキー+メモリスタ+キャパシタ

#### 3-3-1.研究背景と目的

近年、人工知能の研究が盛んに行われていて、その代表的な技術としてニューラルネットワークがある。ニューラルネットワークは、脳の神経回路をもとにした情報処理モデルである。現在、ソフトウェアでの研究が主流となっており、サイズや消費電力などに問題がある。対して、ニューロモルフィックは、ハードウェアで脳を模倣することで小型化・低消費電力化が期待できる。そこで、メモリスタ+キャパシタを用いたニューロモルフィックデバイスの作製を目的としている。

#### 3-3-2. デバイス作製(手順)

- 1.真空蒸着を用いて、下部電極を成膜する

- 2.スパッタリングまたはミストCVDを用いてアモルファス酸化物半導体を成膜する

- 3.真空蒸着を用いて、上部電極を成膜する

- 4.条件に応じて大気アニールを行う

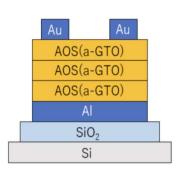

まず酸化膜付きシリコン基板( $SiO_2/Si$ )に下部電極(Al)を成膜し、アモルファス酸化物半導体の成膜を行う。当実験では、アモルファス酸化物半導体としてGTO(Ga-Su-O)やIGZO(In-Ga-Zn-O)を使用している。次に上部電極(Au)の成膜を行う。

必要に応じて、大気アニールによって膜状態の安定化を図る。

アモルファス酸化物半導体の製膜方法には、スパッタリング法とミストCVD法がある。以下では各方法での製膜条件や測定方法をまとめる。

#### 3-3-3.デバイス作製条件(RFマグネトロンスパッタリング)

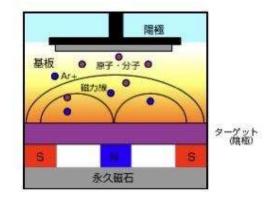

#### ・スパッタリングとは

スパッタリングとは、薄膜形成に用いられる物理的気相成長法(PVD)の1種であり、ターゲット(薄膜形成の材料)とガラスやシリコン基板など(薄膜を形成したいもの)を設置した真空状態のチャンバ内に、不活性ガス(Arなど)を導入する。不活性ガスであるArは、ターゲット側を陰極として高電圧を印加することでAr+となり、Ar+が陰極であるターゲットに引き寄せられて、ターゲットに衝突することで、ターゲット原子/分子が叩き出され、シリコン基板に薄膜が形成される。真空状態で処理を行うため、不純物の少ない薄膜形成ができる。

また、今回用いたRFマグネトロンスパッタリングは、マグネットを接地することで電極近傍の電場と直交する磁場を発生させる。磁場があることにより、磁場に電子が集まり、電子密度の高い空間を作り出すことができ、電子がArに衝突する回数が増え、Ar+の生成が促進される。増加したAr+がマイナスに帯電しているターゲットに引き寄せられてスパッタするため、成膜速度を速くすることができる特徴がある。

(参照:尾池工業株式会社 https://www.oike-kogyo.co.jp/research/column/sputtering/)

# · 作成構造 · 条件

Ar と O2の流量比は $Ar/O_2: 20/0: 20/20: 20/0$  として、GTOの成膜時間の条件を変更

| 材質               | 蒸着時間       |  |  |

|------------------|------------|--|--|

| 金                | 5分         |  |  |

| GTO (20:0)       | 10分 or 5分  |  |  |

| GTO (20:10)      | 15分 or 10分 |  |  |

| GTO (20:0)       | 10分 or 5分  |  |  |

| アルミ              | 5分         |  |  |

| SiO <sub>2</sub> | 酸化膜厚50nm   |  |  |

・大気アニール300℃,20分

#### 3-3-4.測定方法・条件

本実験では以下の測定を行う。

- ・半導体パラメータアナライザでメモリスタのI-Vを測定する。

- 1. 上部電極から下部電極にかけて電圧を加える。

- 2. 出力されるI-Vグラフを確認する。

- 3. データをまとめ、考察する。

- 4. 条件を変えて1~3を繰り返す。

- ・半導体パラメータアナライザで絶縁膜のI-Vを測定する。

- ・電気回路部品を用いてブレッドボード上にニューロンを再現。

- 1. ブレッドボード上に回路を組む。

- 2. 任意波形発生装置を使い、オシロスコープで観察する。

- 3. データをまとめ、考察する。

- 4. 条件を変えて、1~3を繰り返す。

#### 3-3-5 結果(RFマグネトロンスパッタリング)

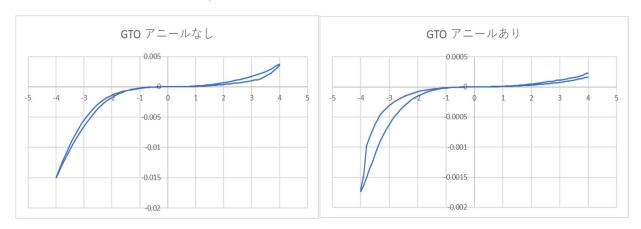

•  $Ar/O_2: 20/0: 20/10: 20/0$ , 15分: 10分: 15分

·Ar/O<sub>2</sub>: 20/0: 20/10: 20/0, 10分: 5分: 10分

上記の図は、各条件のアニールをした場合としなかった場合についてそれぞれ示している。 アニールをすることによって、I-Vグラフの特性(開き)が向上していることが分かる。これは、薄膜の状態が安定化されたことが原因と考えられる。

また、上記の図から20/0:20/10:20/0,10分:5分:10分のときと比較して15分:10分:15分のときの方が、開きが大きくなっており、メモリスタ特性として良い結果が出ていることがわかる。このことから、成膜時間を長くし膜厚が厚くなることで、膜質が安定し、特性が良くなったと考えられる。

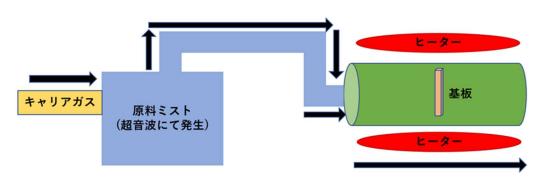

# 3-3-6 デバイス作製 (ミストCVD)

- 1. 原料溶媒を霧状にする

- 2. キャリアガスによって反応部に運ぶ

- 3. 熱分解によって反応させる

#### 良い点

- ・非真空で成膜できる

- ・短時間で製膜可能(現在は5時間程度)

- 安価で製膜可能

# 良くない点

- ・毒性の高いものは成膜できない

- ・(当研究室では)スパッタ法に比べて安定した成膜ができていない

- ・(当研究室では)スパッタ法のものに比べて電気的特性が良くない

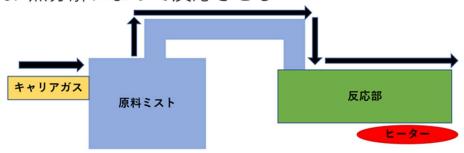

ホットウォール方式

- ・流体が温度の低い方向へ移動する熱泳動を利用

- ・暖かい壁面よりも温度の低い基板へミストガスが流動する

- ・大面積に渡って均質な膜を得ることは難しい

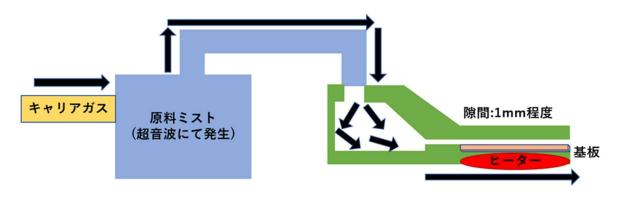

ファインチャネル方式

- ・狭い反応部へ行くと、流体の圧力降下によってミストは重力方向へ行くことから、基板への押し付 け効果が期待できる

- ・反応部が狭いため、気体が効率よく加熱される

# 3-3-7 デバイス構造・条件

# 共通条件

·下部電極: Al 5分間蒸着

·上部電極: Au 5分間蒸着

・GTO: Ga:Sn=1:3(モル比)

モル濃度0.03

キャリアガス:0.5L/min

希釈ガス:10L/min

# 変更した条件

| 条件   | A     | В     | С     | d     |

|------|-------|-------|-------|-------|

| 成膜温度 | 450°C | 400°C | 350°C | 400°C |

| 製膜時間 | 30min | 30min | 30min | 20min |

| 製膜方式 | HW    | FC    | FC    | FC    |

3-3-7.測定方法・条件

上記と3-3-4と同様

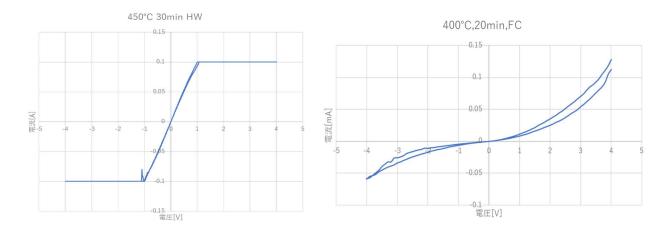

# 3-3-8.結果 (ミストCVD)

#### 上図はIV測定の結果である。

左の図は活動初期に条件1で製膜したものである。この結果から、この条件ではデバイスがショート していて、ヒステリシスが確認できない。

右の図は活動終盤に条件4で成膜したものである。この結果では、ヒステリシスが少し確認できる。 スパッタ法のデバイスに比べてまだまだ電流の値がかなり小さいため、今後は近づけるように最適な 条件を調べていきたい。

# 3-4.北海道大学共同研究

# 3-4-1.研究背景目的

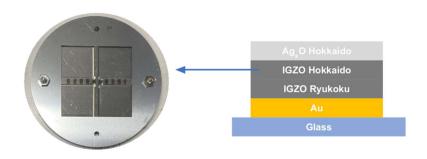

IGZO、酸化銀の界面でショットキー特性を見つける。現状ショットキー特性が見られず、ショットキー特性だけを見るために現在は様々な条件で酸化銀の成膜を北海道大学に依頼し、測定を行っている。

3-4-2.デバイス構造・条件

北海道大学>AgxO(様々な条件)

北海道大学>IGZO上部(様々な条件)

龍谷大学>IGZO下部(様々な条件)

龍谷大学>Au(5min)

# 北海道大学(IGZO + Ag<sub>x</sub>O)

1.5 cm × 1.5 cm 基盤:メタルマスクをつけた状態

{下部電極:Au, IGZO 下層(Ar/O2=20/0), IGZO上層(Ar/O2=20/5)}×4枚

#### 3-4-3.結果

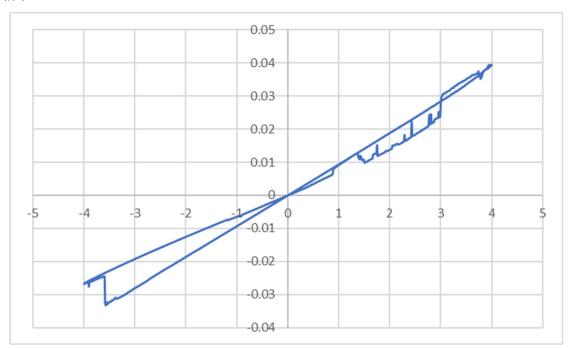

IV特性の測定結果

現状では、酸化銀を成膜してもほぼ完全に導体のIV特性が出てしまう。

今後も実験を続け、ショットキー特性を見つけることを目標に測定を続ける。

また、デバイスを依頼し、届くまでの期間がかなり長いため、ショットキー、キャパシタを除いたメモリスタのみのデバイスの特性も実験していく。

# 3-5.TFT · 強誘電体

#### 3-5-1.研究背景と目的

近年、テレビやスマートフォンは大型化、軽量化、薄型化が進んでいる。現在、ディスプレイの駆 動素子として実用化されているTFTは主に多結晶シリコン(poly-Si)やアモルファスシリコン(a-Si)T FTである。現在、このpoly-Siやa-Siに代わる低温大面積用デバイス材料として酸化物半導体を用いたT FTの研究が盛んに行われている。アモルファス酸化物半導体の代表的な例としてIGZOが挙げられる がIGZOに含まれるInはレアメタルであり安定供給や毒性による取り扱いの問題を抱えている。そこ で、Inと似た電子軌道を持つSnと酸素脱離を抑制するGaに着目し、IGZOの代替としてGa-Sn-O(GT O)を用い、トランジスタ型のFeRAMの実現を目指している。

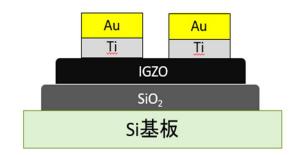

#### 3-5-2.デバイス構造・条件

今回の実験では今後行うGTOでの実験の参考のためにIGZOを用い実験を行った。

SiO2付きSi基板上にIGZOをRFマグネトロンスパッタリング法を用いて成膜し、アニールなし、300℃ アニール、400℃アニールの3つの条件でデバイスを作製した。デバイスの構造とIGZOの成膜条件は以 下の図3-5-1に示す。

# IGZO成膜条件

ガス流量比: Ar/O<sub>2</sub> = 20/1

成膜圧力 : 1[Pa]

成膜時間:5[min]

投入電力:100[W]

# アニール条件

アニール: 大気アニール

アニール時間:300[℃]

ともに60[min] 400[°C]

図3-5-1 実験条件

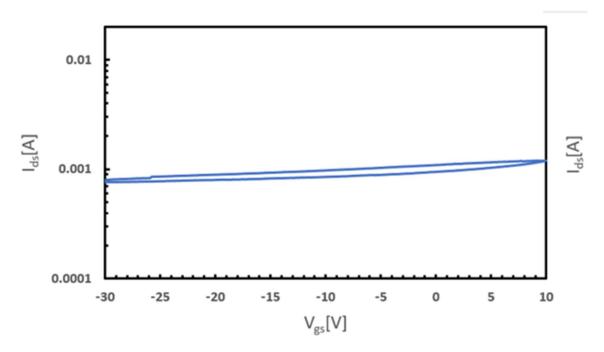

#### 3-5-3. 結果

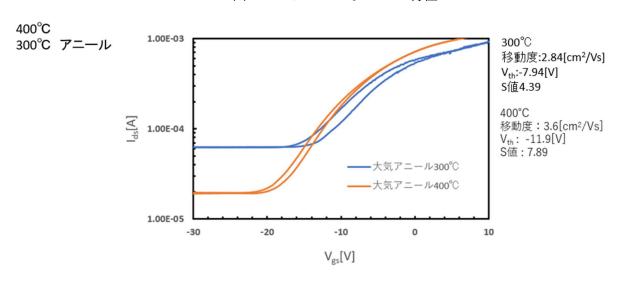

アニールなしの結果を図3-5-2に示し、300[℃]、400[℃]アニールの結果を図3-5-3に示す。

# アニールなし

図3-5-2 アニールなしのI-V特性

図3-5-3 アニールありのI-V特性

アニールをしていないデバイスではI-V特性が見られなかったが、アニールを行ったデバイスでは半導体のI-V特性が観測された。このことからIGZOを用いたTFTではアニールをすることでTFTの性能を向上させることが可能であることが分かる。アニールによりI-V特性が観測された理由としては、アニールすることによりIGZOの結晶化が進んだため電子移動度が向上したためであると考えられる。

しかし、今回のIGZOの成膜条件では $300[^{\circ}C]$ 、 $400[^{\circ}C]$  どちらのアニール温度においても移動度が小さいため、今後はTFTの性能を向上させるためにIGZOの成膜条件を変更し最適化を目指す。

# 3-6. NAIST インターンシップ

# 3-6-1. 実験内容

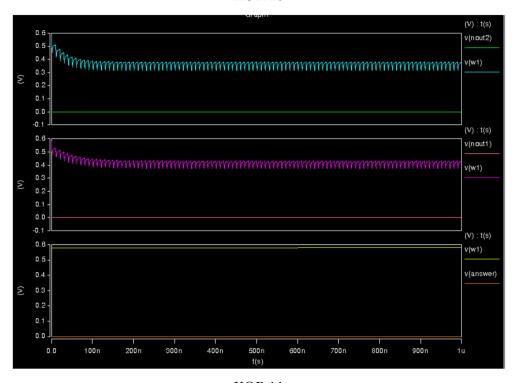

シミュレーションソフト HSPICE 上で電子回路の設計、シミュレーションを行う

# 3-6-3.結果

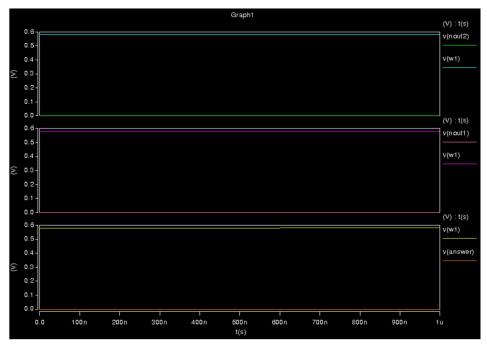

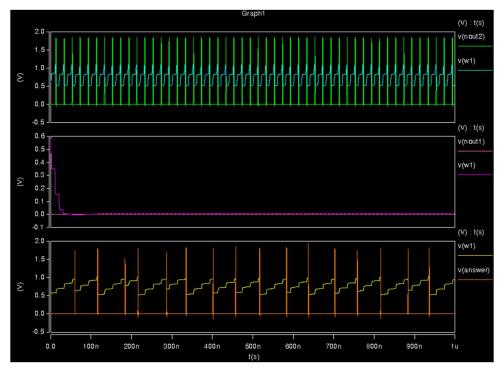

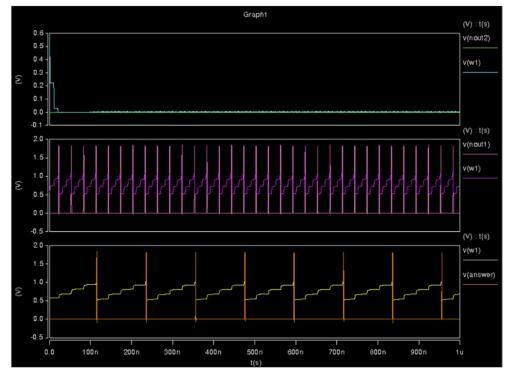

非線形回路の中で基本の形となるXOR回路の作製とシミュレーションを行った。 また、回路設計の基礎とHSPICEの動作方法について学ぶことができた。

XOR 00

XOR 01

XOR 10

**XOR 11**

全ての図に共通して、一番上が"入力2",真ん中が"入力1",一番下が"出力"となっている。 XORでは二つの入力が異なる場合のみに1が出力されるが、図からそれが達成されていることが分かる。

# 3-7.台湾国立成功大学

# 3-7-1.実験内容

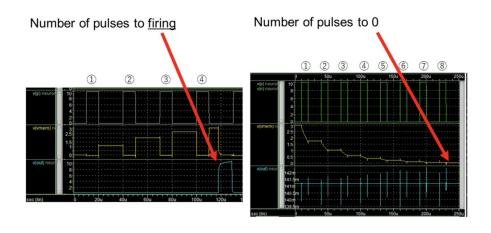

設計された回路に用いられているトランジスタの個数や大きさなどを変化させた際の出力電圧や出 力電流の変化を下記の内容に着目して確認した。

- ・ドレイン電圧の違いによる出力電流の違いを確認

- ・ゲート電圧の違いによる出力電流の違いを確認

- ・インバータによって出力電圧が反転することを確認

- ・Delay unitの動作を確認

- ・TFTのW,L,Mを変化させて、より低電力でDelay unitとして機能する部分を見つける

# 3-7-2.結果

| pluse width | Number of pulses to firing | Number of pulses to 0 | implementor |  |

|-------------|----------------------------|-----------------------|-------------|--|

| 0.000027    | 2                          | 2                     | kawasaki    |  |

| 0.00002     | 2                          | 5                     | DEGUCHI     |  |

| 0.000013    | 3                          | 5                     | kawasaki    |  |

| 0.00001     | 4                          | 8                     | kuwahara    |  |

| 0.000008    | 5                          | 13                    | DEGUCHI     |  |

| 0.000007    | 6                          | 14                    | kakuma      |  |

| 0.000006    | 7                          | 15                    | kitasann    |  |

| 0.0000058   | 7                          | 16                    | kakuma      |  |

| 0.0000055   | 7                          | 17                    | kakuma      |  |

| 0.000005    | 8                          | 17                    | HORIUTI     |  |

| 0.0000045   | 9                          | 21                    | nemoto      |  |

| 0.000004    | 10                         | 21                    | HORIUTI     |  |

| 0.0000035   | 11                         | 26                    | kawasaki    |  |

| 0.000003    | 13                         | 35                    | nemoto      |  |

| 0.000002    | 20                         | 53                    | nemoti      |  |

| 0.000001    | 41                         | 80                    | kakuma      |  |

| 0.0000009   | 46                         | 92                    | HORIUTI     |  |

| 0.0000002   | NA                         | NA                    | HORIUTI     |  |

| No. | J:##       | Amount of rising | Amount of falling | Resista | Resistance size |             |

|-----|------------|------------------|-------------------|---------|-----------------|-------------|

|     | difference |                  |                   | R1      | R2              | implementor |

| 1   | 0.33       | 1.35             | 1.02              | 2000000 | 2500000         | nemoto      |

| 2   | 1.32       | 1.32             |                   |         |                 |             |

| 3   | 0.28       | 1.35             | 1.07              | 2000000 | 2500000         | kuwahara    |

| 4   | 0.38       | 1.34             | 0.96              | 2000000 | 2500000         | kawasaki    |

| 5   | 0.43       | 1.32             | 0.89              |         |                 | kita        |

| 6   | 0.26       | 1.35             | 1.09              | 2000000 | 2750000         | kuwahara    |

| 7   | 0.35       | 1.35             | 1                 | 2000000 | 2300000         | nemoto      |

| 8   | 0.18       | 1.35             | 1.17              | 2000000 | 4000000         | kuwahara    |

| 9   | 0.39       | 1.33             | 0.94              | 2500000 | 2000000         | deguchi     |

| 10  | 0.25       | 1.35             | 1.1               | 2000000 | 3500000         | nemoto      |

| 11  | 0.11       | 1.35             | 1.24              | 2000000 | 6000000         | kuwahara    |

| 12  | 0.39       | 1.31             | 0.92              | 2000000 | 3000000         | kita        |

| 13  | 0.07       | 1.35             | 1.28              | 2000000 | 8000000         | kuwahara    |

| 14  | 0          |                  |                   | 2000000 | 2500000         | kakuma      |

| 15  | 0.08       | 1.35             | 1.27              | 2000000 | 8000000         | nemoto      |

| 16  | 0.08       | 1.35             | 1.27              | 2000000 | 2500000         | horiuti     |

| 17  | 0.03       | 1.35             | 1.32              | 2000000 | 10000000        | kuwahara    |

| 18  | 0.02       | 1.35             | 1.33              | 2000000 | 11000000        | kuwahara    |

| 19  | 0          |                  |                   | 2000000 | 5000000         | kawasaki    |

| 20  | 0.05       | 1.35             | 1.3               | 2000000 | 14000000        | nemoto      |

| 21  | 0.41       | 1.35             | 0.94              | 3000000 | 2500000         | horiuti     |

| 22  | ^          |                  |                   |         |                 |             |

正と負の電圧を入力した際に、正と負の入力電流の値の差をできるだけ小さくするような、抵抗値を見つけるために、それぞれの入力付近についている抵抗の値を変化させた。

結果から、今回の回路では正電圧側の抵抗値を $20000000\Omega$ としたとき、負電圧の抵抗値を5倍ぐらいにしたとき、差が最も小さくなることがわかった。

なお、中川については、急な都合により、台湾国立成功大学での活動に参加できなかったが、代わりに国際会議IDWでの研究紹介の活動をすることとなっている。

#### 4.まとめ

今回私たちは、木村睦研究室の活動やNAISTのインターンシップを通じて薄膜デバイスとニューロモーフィックシステムの調査・研究を行った。次世代の不揮発性メモリやニューロモーフィックコンピュータの研究は今後の情報化社会にとって重要なものであり、その実現に向けて努力したいと考える。今回の研究報告を経て、これからの研究でより踏み込んだ研究を行いたいと思う。