# 特集 学生の研究活動報告 - 国内学会大会・国際会議参加記 34

# AM-FPD 21 に参加して

—Non-volatile memory using a Ga-Sn-O TFT with a stacked gate insulator film of SiO<sub>2</sub> and (Bi, La)<sub>4</sub>Ti<sub>3</sub>O<sub>12</sub>—

> 福井智貴 Tomoki FUKUI 電子情報学専攻修士課程 1年

## 1. 緒論

近年、テレビやスマートフォンの薄型化、軽量化、高画質化、さらに大面積化が進んでいる。この発展には液晶ディスプレイに不可欠な駆動素子として使用されている薄膜トランジスタ(TFT)が重要な役割を果たしている。また TFT の中でも Si, 有機半導体に続く新しい低温大面積用デバイス材料として、酸化物半導体を用いた TFT の研究が盛んに行われている。現在は In-Ga-Zn-O(IGZO) を用いた TFT の研究開発、実用化が進んでいる。しかし、In は希少金属であるため、資源枯渇、安定供給、さらに毒性があるなどの問題が考えられる。そこで我々は Sn (スズ) は In と近い電子軌道を有している Sn に着目した。

以上の理由から Ga-Sn-O(GTO) に着目した. GTO 薄膜はレアメタルの使用量減少かつ高移動度 を実現することができる.

本研究では、ゲート絶縁膜が2層の TFT を作製した.このことからオン電流が小さくなる可能性がある.そこで(Bi, La) $_4$ T $_i$ O $_1$ 2(BLT)を使用した.この強誘電体である BLT は Bi 層状疑似ペロブスカイト型酸化物に分類される.これらの特徴としてリーク電流が小さい、薄膜化した時の特性劣化が少ないということが挙げられる.さらに、BLT は自発分極によって少ないキャリア移動度でも大きなオン電流を得ることができることも理由の1つである.これらの特徴からゲート絶縁膜に使用できると考えた.

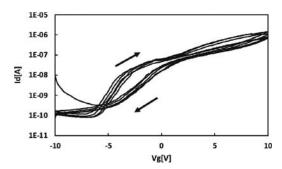

今回の研究からポストアニール 300℃ で移動度 2.13 cm<sub>2</sub>/Vs, SS 値 1.08 V, しきい値電圧 V<sub>th</sub> 6.08 V, オン電流  $I_{ON}$  1.5 mA, ヒステリシス幅 4.8 V の TFT 特性, 時計回りのヒステリシスを確認した.

#### 2. 作製手順

熱酸化膜付き Si 基板に BLT を RF マグネトロンスパッタリング法によって表 1 の条件で成膜した後、表 2 の条件で段階的にアニール処理を行った.ここで BLT の結晶構造を XRD によって解析した.次にメタルマスクを基板に取り付け、GTO を RF マグネトロンスパッタリング法によって表 1 の条件で成膜した.次に電極として Ti, Au を真空蒸着法によって 5 min ずつ堆積させた. その後、ポストアニールを  $100\sim400$ ℃ で 60 min 行った. そして測定した基板の  $I_{D}$ -V<sub>G</sub> 特性と保持特性を半導体パラメータアナライザ(Agilent Technologies 4156 C)で測定した.

表1 成膜条件

|                                         | BLT       | GTO       |

|-----------------------------------------|-----------|-----------|

| temperature $[\mathcal{C}]$             | Room temp | Room temp |

| Film formation pressure [Pa]            | 0.66      | 0.66      |

| Input power [W] (Target size: φ2"x 5 t) | 60        | 60        |

| Ar/O <sub>2</sub> [sccm]                | 20/2.7    | 20/1      |

| Film formation time [min]               | 60        | 5         |

表 2 BLT のアニール条件

|                  | temperature $[^{\circ}C]$ | Time [min] |

|------------------|---------------------------|------------|

| 1-step annealing | 550                       | 60         |

| 2-step annealing | 650                       | 60         |

| 3-step annealing | 750                       | 60         |

#### 3. 結果

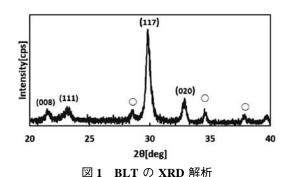

まず BLT 膜について 750℃ の 1 段階アニール, 550℃ と 750℃ の 2 段階アニール, 550℃ と 650℃ と 750℃ の 3 段階アニールの基板を XRD で解析 し、3 段階アニール基板の結果を図 1 に示す.

図1の○マークが常誘電体相であるパイロクロア

相のピークを示している. これらの図から (117) のピークはすべてのサンプルから確認できた. さら に段階的にアニールを行うことによって (008), (111), (020) のピークを確認することができた.

次にポストアニールが及ぼす影響について調査するためにアニールなしから 400  $\mathbb{C}$  までの温度で  $I_{D-}$   $V_{G}$  特性を調べたところポストアニール 300  $\mathbb{C}$  の結果として図 2 が得られ、まとめると表 3 のような結果が得られた.

100℃ 200℃ 300℃ 400℃ Non ann Mobility 1.26 0.74 2.13 1.64  $[cm^2/Vs]$ ss [v] 1.47 1.22 1.08 1.56  $V_{th}$  [V] 3.96 3.84 6.08 7.64 Hysteresis 1.7 1.5 4.8 2.4 width [V] Ion [mA] 0.024 0.30 0.11.5

表3 本研究で得られた値

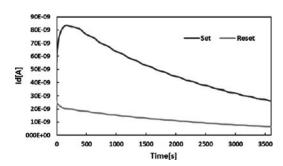

図 3 に 300 $^{\circ}$  でアニールしたサンプルの保持特性 のグラフを示す。セットはゲート電圧に-10 V を 30 秒間印加した後の状態,リセットはゲート電圧 に 10 V を 30 秒間印加した後の状態である。図 3 にゲート電圧 0 V とドレイン電圧 10 V を加えたときの電流値を示す。

### 4. 考察

表3で得られたオン電流が小さかった。これは

図 2 ポストアニール 300°C サンプルの I-V 特性

図3 ポストアニール 300℃ サンプルの保持特性

BLT の強誘電性が低かったことが原因だと考えられる。図1に見られたパイロクロア相は低酸素の成膜条件に変更することで改善できると考えている。また得られた SS の値が高いことが確認された。これは GTO の膜厚に起因していると考えている。膜厚を薄くすることでオフ状態のときに完全に空乏化させることができ、さらに素早くオン状態に切り替えることができれば、今回のサンプルよりも急峻な立ち上がりが得られるのではないかと考えている。図3で60分間は保持特性が得られたが、フローティングゲートメモリとして機能しているかは、今後さらなる調査が必要である。

#### 5. 結論

3 段階アニール処理をした BLT 膜が良好な結晶性を示した. ポストアニール 300℃ のサンプルが一番良い特性を確認できた. フローティングゲートメモリとしての応用はさらなる調査が必要である.