# 特集 学生の研究活動報告 - 国内学会大会・国際会議参加記 29

# AM-FPD'18 に参加して

杉 崎 澄 生 Sumio SUGISAKI 電子情報学専攻修士課程 2年

# 1. はじめに

7月3日~6日に、龍谷大学アバンティ響都ホールで行われた THE 25th INTERNATIONAL WORK-SHOP ON ACTIVE-MATRIX FLATPANEL DIS-PLAYS AND DEVICES (AM-FPD'18) に参加し、「Room Temperature Fabrication of Variable Resistive Memory Using Ga-Sn-O Thin Film」という題目で発表を行った。

# 2. 研究内容

#### 2.1 研究背景

非結晶酸化物半導体を活性層として用いた薄膜トランジスタは a-Si 薄膜トランジスタと比較して 10 倍高い電界効果移動,低リーク電流,高い ON/OFF 比と非常に優れた電気的特性を示す.また,低温での作製も可能であることからプラスチック基板にトランジスタを作製することでフレキシブルデバイスへの応用も期待されている.しかし,より高性能なフレキシブルデバイスのためにはメモリについても高品質であり,低温で作製しなければならない.本研究ではトランジスタとメモリの低温での作製を目指している.そこで,非結晶酸化物半導体の一つであり,低温でのトランジスタ動作が確認されているガリウムとスズで構成された Ga-Sn-O(GTO)に着目し,GTO 薄膜を用いた抵抗変化型メモリの室温での作製を行った.

## 2.2 作製条件

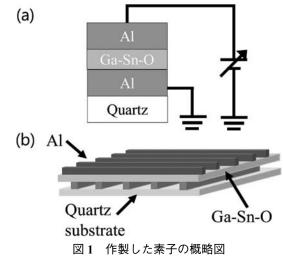

石英を基板とし、下部電極としてアルミニウムを 熱蒸着法で成膜を行った。次に抵抗変化層として、 RF マグネトロンスパッタリング法で GTO 薄膜を 成膜した。成膜条件は成膜時間 3 min, 投入電力 60

(a) 断面の概略図 (b) 全体の概略図

W ガス流量比  $Ar/O_2 = 20/1$  sccm である。最後に上部電極としてアルミニウムを下部電極と同様に成膜した。図 1 (a) に作製した素子の断面概略図を示す。図 2 (b) に作製した素子の全体概略図を示す。今回,作製した素子はクロスポイント構造の素子であり,高集積化や高速動作において他の構造のデバイスと比較して有利である。

# 2.3 実験結果

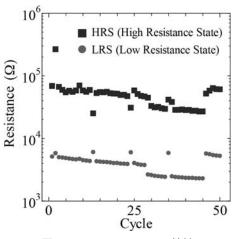

今回,作製した素子に 50 回繰り返し,書き込みと消去を行った電流 -電圧特性を示す.図 2 (a) に 1 回目と 50 回目のメモリ特性の線形グラフ,図 2 (b) にメモリ特性の対数グラフを示す.また,実線が 1 回目,破線が 50 回目のグラフである.図 2 (a) から 50 回の繰り返し書き込みと消去を行ってもメモリとしての機能を確認することができる.図 2 (b) から 2 V 付近から抵抗値の変化が始まっていることがわかる.図 3 に電圧 1 V の時の,高抵抗状態(High Resistance State)と低抵抗状態(Low Resistance State)との抵抗の値を示す.図 3 から 50 回サイクルを繰り返し行ってもメモリ特性を維持していることがわかる.50 回目において高抵抗状態は 60.3 k $\Omega$ ,低抵抗状態は 5.26 k $\Omega$  であり,ON/OFF比は 10 を維持していることがわかる.

図2 メモリ特性の電流一電圧特性 (a) 線形グラフ (b) 対数グラフ

#### 2.4 まとめ

GTO 薄膜を抵抗変化層、電極にアルミニウムと した Al/GTO/Al セル構造のクロスポイント型抵抗 変化メモリを作製し十分なメモリ特性を得ることに 成功した。また、低温プロセスであり、既存の薄膜

図3 メモリのサイクル特性

トランジスタの作製プロセスと親和性が高い方法で作製することができた.今後は、トランジスタのチャネル層とメモリの抵抗変化層を同時に成膜することでトランジスタとメモリの同一基板での同時作製を目指して研究を行っていく.

## おわりに

今回の発表で国内外から多くの人と議論することができ、とても有意義な時間であり、多くの助言をいただくことができました。この最後に、今回の発表を行うにあたって、有益な議論をしていただいた、奈良先端科学技術大学院大学物質創成科学研究科上沼睦典助教、国立研究開発法人物質・材料研究機構 ナノファブリケーショングループ生田目俊秀グループリーダー、龍谷大学 革新的材料・プロセス研究センター 客員研究員松田時宜博士に深く感謝します。